Hay varias maneras de proteger un circuito contra las descargas electrostáticas (ESD). Como estrategia general, se puede usar una serie de componentes de protección en la tarjeta de circuito impreso para proteger el producto final de una ESD. Estos componentes de protección pueden ser: resistencias en serie, condensadores, vías de chispas, cuentas de ferrita, filtros de interferencia electromagnética y supresores de tensión transitoria (TVS).

En este post nos centraremos en las protecciones más sencillas: resistencias en serie, condensadores y vías de chispas … (Leer más)

RESISTENCIA EN SERIE

Los circuitos integrados (CI) tienen protecciones internas contra las ESD en sus entradas diodos. Son diodos de protección tipo “CLAMP” porque limitan la tensión de entrada entre VCC y masa (más la tensión del diodo). Supongamos por ejemplo que los diodos internos de protección contra ESD de un CI tienen una intensidad máxima absoluta de +/- 2 mA. Supongamos también que la diferencia máxima entre la tensión de alimentación (VCC) y la unidad de E / S es de 0,3V. Podemos añadir una pequeña resistencia en serie como protección contra las ESD. En este caso, la resistencia en serie debe ser mayor de 0,3V / 2mA = 150 ohmios.

No se debe exceder ninguno de los parámetros máximos absolutos. La corriente debe estar dentro de los límites y al mismo tiempo la tensión no debe exceder los límites entre -0,3V y (0,3V + VCC). Exceder uno de los límites puede afectar al funcionamiento del CI.

Entonces, (5V – 3,3V – 0,3V) / 4K7 = 1,4 V / 4K7 = 0,3 mA, este circuito debería ser correcto. Esta especificación de la intensidad es correcta (está dentro de los 2 mA), pero se viola la especificación de tensión en la patilla (Vpatilla > 0.3V + VCC). La tensión máxima es (VCC + 0,3V) , ya que cualquier tensión más alta elevaría la corriente del diodo protector a valores casi ilimitados. Si se mantiene la corriente por debajo de 2 mA, la tensión nunca aumentará por encima de (VCC + 0,3 V, y si se mantiene la tensión por debajo del límite, la corriente nunca aumentará.

Añadir una resistencia en serie provocará una caída de tensión de 1,4 V con una corriente de 2 mA , R = 1,4 V / 2 mA = 700 ohmios. Ni la corriente ni la tensión estarán fuera de los límites del CI. Pero esto es un error de cálculo. La corriente de entrada normal en las patillas de E/S suele ser algunos órdenes de magnitud más pequeña. Solo comienza a aumentar cuando casi se llega al límite de tensión. Por lo tanto, en una resistencia de 700 óhmios , caerán 1,4 V circulando la corriente máxima de 2 mA. Pero con el uso de una resistencia de 17 K la intensidad será de 100 microamperios, que es suficiente para la entrada. La resistencia en serie mínima absoluta es de 700 ohmios, pero también se puede usar una resistencia de 17K y seguirá funcionando bien. Es recomendable utilizar mayor (17K) para reducir el consumo.

Otro aspecto a considerar es por dónde circula la corriente. Una intensidad de 2 mA por patilla solo causará, con la resistencia de 700H, P = R x I2 = 700H x (2mA)2 = 2,8 mW de potencia, pero estos 2 mA fluirán hacia VCC. Ahora bien, VCC generalmente está generada por un regulador de tensión y estos reguladores solo pueden limitar la cantidad de corriente que sale desde la tensión de salida del regulador. Lo mejor que estos reguladores pueden hacer es cortar la circulación de corriente de la tensión de salida por completo, pero no pueden absorber ninguna corriente desde la salida si llegara a ser mayor que la tensión de salida deseada. Pero esto es lo que sucede cuando la corriente circula a través de los diodos. Si los circuitos alimentados por VCC no consumen al menos la corriente que circula hacia VCC a través de los diodos de protección, VCC comienza a aumentar, hasta que la corriente de entrada y el consumo del circuito sean iguales. Esto puede superar fácilmente la VCC máxima y destruir el CI (pero no es tan fácil).

CONDENSADOR

El uso de un condensador como protección contra las ESD también es una solución económica al problema. A continuación se muestra un circuito típico en el que se añade un condensador cerámico a una patilla de un CI para protegerla contra las ESD.

Esta protección se basa en la conservación de la carga. El condensador es capaz de almacenar carga eléctrica entre sus placas. Si caminamos sobre una alfombra, acumulamos carga en nuestro cuerpo. El cuerpo tiene una capacidad. Cuando tocamos la patilla expuesta, la carga acumulada en nuestro cuerpo se descargará a la patilla y al condenador.

En el modelo de la ESD, CESD es la capacidad del cuerpo humano, mientras que VESD es la tensión de pico en esta capacidad. Un modelo de ESD usual, es CESD = 330pF y VESD = 8kV. Cuando caminamos sobre una superficie alfombrada, la carga adquirida en el cuerpo puede considerarse como la carga inicial. A partir de la ecuación de carga Q = CV, podemos formular la siguiente ecuación basada en el diagrama anterior: Qinicial = CESD x VESD

Cuando tocamos la patilla expuesta, la carga del cuerpo humano se transfiere a la patilla y al condensador conectado a ella. Si observamos el circuito equivalente, la carga final será:

Qfinal = Cfinal x Vfinal

Cfinal es la combinación en paralelo de C1 y CESD y Vfinal es la tensión equivalente en la patilla. Ésta es también la tensión en el condensador C1:

Cfinal = C1 + CESD

En virtud de la conservación de las cargas: Qinicial = Qfinal y CESD x VESD = Cfinal x Vfinal

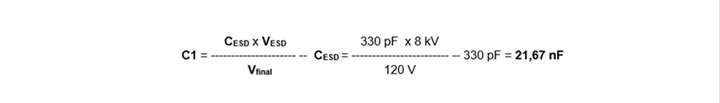

Vamos a ver un ejemplo con el modelo de ESD anterior (CESD = 330pF, VESD = 8kV). Calculamos el valor de un condensador cerámico necesario para proteger el patilla expuesta del CI, que puede soportar solo una sobretensión de 200V. La solución no es buena si usamos directamente los 200V; en su lugar consideraremos un margen. Como regla general, solo podemos usar el 60% de los 200V, que son Vfinal = 120V. Así,

El valor estándar más cercano es 22nF. Un valor de 22nF para C1 dará un tensión en la patilla de:

Por lo tanto, debemos usar un condensador cerámico de 22nF con una tensión nominal de 200V en la patilla expuesta del CI. La protección contra las ESD de un condensador puede ser efectiva en aplicaciones que no requieren una respuesta muy rápida. Sin embargo, en aplicaciones que requieren una respuesta muy rápida, un condensador puede no ser adecuado, ya que introducirá un retraso significativo en la señal de la patilla.

VÍAS DE CHISPA

Otra forma simple de reducir el riesgo de fallos graves ante las ESD es colocar dispositivos de protección en el camino de la corriente de la ESD.

Para reducir los costos y ahorrar espacio en los circuitos impresos, se pueden usar vías de chispas. Hay diferentes estructuras de protección contra las ESD utilizadas en los circuitos impresos, por ejemplo, vías de chispas que protegen los componentes durante el montaje de los circuitos impresos utilizando un trazado de masa en "forma de dedo" o algunas protuberancias similares a los dientes a lo largo del recorrido del conductor. Sin embargo, la tensión de ruptura de las vías de chispa no es lo suficientemente baja, y el retraso es demasiado largo.

Una vía de chispas es un dispositivo mecánicamente simple, pero eléctricamente complejo. Los aspectos importantes de las vías de chispa son:

Tensión de ruptura de CC:

La curva de Paschen representa la tensión de ruptura de un espacio con diferentes longitudes de arco, bajo las siguientes condiciones: presión normal del aire y campo homogéneo. Se ha demostrado que la curva de Paschen también es un buen predictor de pequeñas vías que tienen un campo eléctrico no homogéneo, como una vía en un circuito impreso. Para un espacio de 0,1 mm, la tensión de ruptura estática es de alrededor 1000 V.

Usando la ley de Paschen, se calcula la tensión de ruptura de CC: Vd = 25,4 x d + 6,64 x d1/2

Por ejemplo, para d=0,1 mm, Vd = 918 V

La longitud del arco o chispa está limitada por el proceso de fabricación hasta una tensión de aproximadamente 1500V. Usando un impulso de aproximadamente 12 ns, no salta la chispa. A aproximadamente 2000 V a través de la vía, utilizando un impulso de 12 ns, se observan las primeras chispas. Para una tensión de 3100 V, casi todos los impulsos generan chispas. Con intensidades de campo promedio de 300 kV / cm, el intervalo de tiempo suele ser muy corto.

Retraso del encendido (retraso estadístico):

El encendido de la chispa puede no ocurrir instantáneamente después de aplicar una tensión mayor que la tensión de ruptura estática. El encendido de la chispa se retrasa hasta que los electrones pueden iniciar el proceso de avalancha, que se denomina retraso estadístico. Si queremos proteger un circuito, la vía de chispa no tendrá efecto como dispositivo de protección hasta después de un lapso de tiempo. Por lo tanto, el lapso de tiempo debe ser lo más corto posible y la tensión de ruptura lo más baja posible. Cuanto más alta sea la sobretensión en la vía de chispas, más rápido será el encendido.

Tensión de encendido:

La tensión de encendido usualmente se sitúa en el margen de 25 a 40V. La consecuencia es que el espacio de la vía de chispas no puede limitar la tensión a ninguna tensión inferior a la tensión de encendido

Las ventajas del uso de las vías de chispa: son baratas y pequeñas, pueden manejar corrientes muy altas y no agregan capacidad, por tanto, no ralentizan la velocidad de la señal. Las desventajas son: la tensión de encendido es alta, el retraso es prolongado, la vía de chispas no tiene efecto como dispositivo de protección hasta que no provoca el encendido de la chispa,

CONCLUSIONES

Los tres tipos de protección contra ESD: resistencia en serie, condensador o vía de chispas son simples, baratos y fáciles de usar. Las otras protecciones como las cuentas de ferrita, los filtros de EMI y los supresores de tensión transitoria (TVS) son algo más caros y ocupan más espacio en el circuito impreso.

REFERENCIAS:

- Jing Li, “The Application of Spark gaps on Audio Jack for ESD Protection”, EMC Laboratory, Missoury University od Science and Technology

- Jens-Michael Gross, “MSP430F47187: clamp diodes on terminals?”, MSP low-power microcontrollers

- Kemet Engineering Center, “Capacitors Can Help With ESD Too”

AUTOR:

Francesc Daura Luna, Ingeniero industrial. Director de la Consultoría de compatibilidad electromagnética LEEDEO/CEMDAL.

Más información: info@leedeo.es , contacto@cemdal.com

Escribir comentario